The К1100СК2B is a monolithic sample-and-hold (SHA) circuit, controlled by signal LOGIC, stores the instantaneous values of the input signal and for a certain time maintain a constant DC voltage at the output with a high accuracy.

The wide bandwidth allows the K1100CК2B to be included inside the feedback loop of 1 MHz op amps without having stability problems. Input impedance of 1010Ω allows high source impedances to be used without degrading accuracy.

The overall design ensures no feedthrough from input to output in the hold mode, even for input signals equal to the supply voltages. Logic inputs on the K1100К2B are fully differential with low input current, allowing for direct connection to TTL, PMOS, and CMOS. Differential threshold is 1.4 V. The K1100CК2B will operate from ±5V to ±15V supplies.

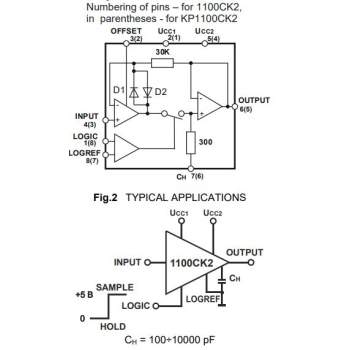

The K1100CК2B OUTPUT tracks the INPUT signal by charging and discharging the hold capacitor (CH). The OUTPUT can be held at any given time by pulling the LOGIC input low relative to the LOGIC REFERENCE voltage and resume sampling when LOGIC returns high. Additionally, the OFFSET pin can be used to zero the offset voltage present at the INPUT.

The nominal value of the supply voltage UСС1,2=±12V for К1100СК2B.

Supplied in TO5-8.